이번 정리에서는 Package에서 Chip과 System이 결합할 때 가장 중요한 기술인 Bonding 기술에 대해서 설명드리고자 합니다. Bonding 기술 중에서 Wire Bonding, Flip Chip Bonding에 대해서 다루고자 합니다.

- 패키지 구조

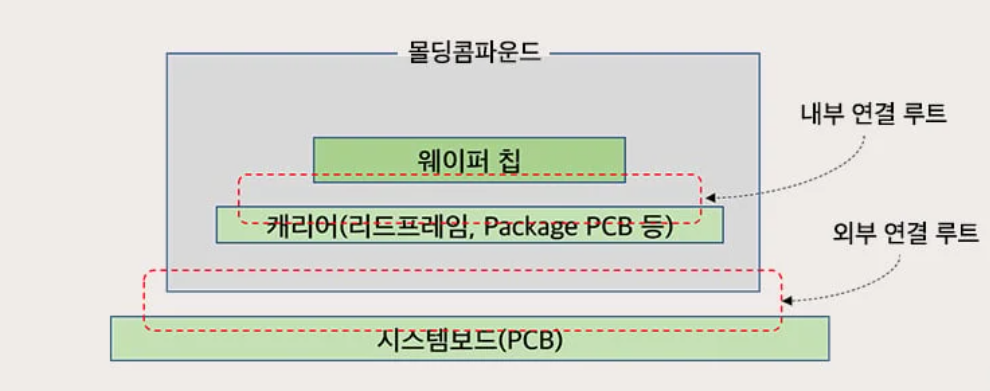

패키지는 기본적으로 그림과 같은 구조로 표현할 수 있습니다.

웨이퍼 칩을 내부 연결 루트를 통해 Substrate와 같은 기판에 연결한 후 Molding을 진행해 하나의 Package로 제작합니다.

그후 외부 연결 루트를 통해 System과 연결하는 구조입니다.

이 과정 중에 연결 루트에 따라서 Package의 이름이 바뀌게 됩니다. Wire Bonding을 사용하면 Wire Bonding Package, Flip Chip Bonding을 사용하면 FCBGA와 같이 이름을 지어주게 됩니다.

과거에는 Lead Frame, 삽입실장, Wire Bonding을 연결하는데 주로 사용했다면,

현재에는 Solder Bump나 Ball, 표면실장 기술을 연결하는데 주로 사용하고 있습니다.

왜냐하면, Bump나 Ball은 전기적으로 연결하는데 있어 최소경로로 연결할 수 있어, 전기적 특성이 좋고, 또한 Ball을 통해 결합력을 높일 수 있기 때문입니다. 또한 Attach가 편리해 교체에 있어서 강점을 가지고 있습니다.

Wire Bonding에 비해 Flip Chip Bonding의 강점

- 전기적 신호 전달 최소화로 전기적 특성 향상

- 신호선의 안정화로 좋은 임피던스 유지

- Package 크기 최소화

1. Wire Bonding

Wire Bonding은 말그대로 기판과 Chip을 Wire를 통해 연결하는 기술입니다.

Wire를 통해 전기적으로 연결하다 보니, 끊어지기 쉬운데 이를 해결하기 위해 재질과, 본딩 조건, 접합 위치를 고려해서 설계를 진행합니다.

- Wire Bonding 공정:

1. 1차본딩(Wire 접합강도 및 신뢰성 결정/ Ball Bonding)

2. Ball Neck(Loop의 높이 결정, 말 그대로 Wire의 안정성을 고려) & Loop Span(긴 루프 일수록 좋은 루프 특성을 고려하는 작업) 생성

3. 2차본딩(Stitch Bond, 접합강도 및 신뢰성 결정/ Tail Length를 균일하게 유지하는 것이 중요)

- 접합 방식

열을 이용해 Bonding하는 열 압착 방식, 초음파를 이용해 Bonding하는 초음파 방식이 있지만, 둘 방법에는 모두 장단점이 있습니다. 열만 이용하면 모양에 변형이 발생할 수 있고, 초음파만 이용하면 시간이 느리고 접합강도가 약해질 수 있습니다. 이를 해결하기 위해 열 압착과 초음파방식을 결합한 열초음파 방식을 현업에서 많이 사용하고 있습니다.

- 신뢰성 평가

1. Wire 당김 시험: Wire를 당겨 Wire의 변형량, 응력값을 측정하는 시험

2. 볼 전단 시험: 1차본딩의 접합 계면, Ball 상태를 파악할 수 있는 시험

2. Filp Chip Bonding

Chip을 뒤집어서 Chip 뒷면에 Bump를 연결하여 기판과 연결하는 방식입니다.

Bump를 통해 수직으로 연결하다 보니, 최소 길이로 연결할 수 있어 전기적 특성이 좋습니다. 또한, Chip 크기만큼만의 작은 사이즈로 제작이 가능하고, Chip 면적에 모든 부분을 I/O로 활용이 가능해 비용이 절감되고 높은 I/O를 가질 수 있습니다. 이는 인덕턴스 , 딜레이, 저항, 열에 대한 모든 지표의 성능을 향상시킬 수 있습니다.

- Flip Chip 공정

1. UBM(Under Bump Metallurgy)형성(접착을 용이하게 만들어주고, 칩확산 방지층, 산화방지층을 형성)

2. Solder Bump 형성(5~10um, 물리적 칩 지탱 + 전기적 연결) & Reflow(Bump에 열을 가해 접합시키는 작업)

3. Solder Joining(IC Chip에 올려 접합 강도 향상)

4. Under Fill(Bump 사이의 빈공간을 채우는 작업)

- Bump 형성 공정

Evaporating(Bump를 Solder에 올리는 작업, 이후 UBM 형성/ 가격이 비쌈)

Electro Plating(강한 접창성을 제공, Diffusion Barrier 형성 작업/ 가격이 저렴하지만 신뢰성이 안좋다는 단점)

Solder Paste Printing(Wire Bonding 공정의 진화 단계로 Paste를 통해 형성)

다음 정리는 추가적으로 표면실장 기술의 솔더링 및 기타 본딩에 관련하여 작성하도록 하겠습니다!

'반도체 패키지 > Advanced Package(AVP)' 카테고리의 다른 글

| HBM3E의 AP-FoM(TSMC) 기반 성능 평가 및 분석 (2) | 2024.06.16 |

|---|---|

| (삼성전자)HBM 16H Stacking을 위한 D2W HCB(하이브리드 본딩) (0) | 2024.06.13 |

| 표면실장 기술 - Soldering & 기타 Bonding (0) | 2024.01.19 |

| 패키징(Packaging) 공정 프로세스 (0) | 2024.01.13 |

| Advanced Package(AVP) 기초 (0) | 2024.01.13 |