1. 후공정 개략도

전공정을 거친 Wafer가 TSP총괄, AVP사업부에 도착하면, 이를 패키징을 진행합니다.

TSP총괄은 Wafer를 Dicing 한 후 Chip을 하나하나 분리하여 진행하는 Conventional Package 입니다.

AVP사업부는 Wafer 전체를 패키징을 진행한 후 Dicing을 진행하는 Wafer Level Package(WLP)라는 차이점이 있습니다.

각각의 공정 마다 장단점이 있습니다. Wafer Level Package는 한번에 Packaging을 진행하기 때문에 가격을 절감하고, 공정 시간을 단축할 수 있습니다. 하지만, Wafer 전체를 Packaging 하기 때문에 Chip 별로 휨현상이 쉽게 발생합니다. Conventional Package는 Chip을 전부 Dicing 한 후 Packaging을 진행하기 때문에 원하는 제품을 원하는 만큼 생산할 수 있다는 장점이 있지만, 하나하나 공정을 진행해야한다는 점에서 생산성이 떨어진다는 단점이 있습니다.

2. 후공정 순서

1. Lamination: 회로가 새겨진 Wafer 위에 테이프를 붙이는 작업, 물리적/화학적 손상을 방지하기 위한 공정

2. Back Grind: Wafer 뒤쪽 표면을 깎아내는 작업, 원하는 크기의 Chip을 제작하기 위해 진행하는 공정

3. Wafer Saw: Wafer를 낱개(Die)로 잘라 나누는 공정

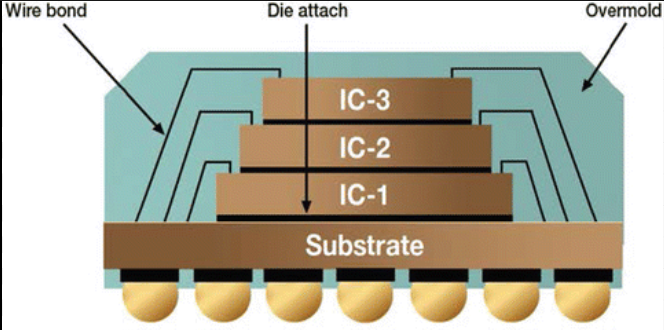

4. Die Attach: Die를 기판 위에 부착하는 공정, 패키지 구조와 Stack 결정 단계이며, 정전기를 방지도 중요하다.

5. Bonding: Chip이 외부와 전기적 신호를 주고 받을 수 있게 구조를 형성하는 공정

6. Molding: Chip과 기판을 외부로 부터 보호하는 Epoxy 수지를 형성하는 공정

7. Marking: SilkScreen 또는 Line을 형성하는 공정, 일련번호나 회사명, 제품명 등

8. Solder Ball Mount: Solder Ball 형성 공정, Solder Ball을 Chip에 안착 후 열을 가해 가열한 후 접합시키는 과정

9. Singulation: 기판 낱개로 분리하는 공정

3. 후공정 기본 개념

- Back Grinding:

전공정을 거친 Wafer의 후면을 원하는 크기만큼 얇게 갈아내는 단계로, 얇게 만든 만큼 Chip의 집적도를 높이고 Stacking이 쉽습니다.

- 공정 프로세스: 테이프 Lamination -> Back Grinding -> CMP -> Wafer Mounting

테이프를 통해 앞면을 보호하고, 휨을 방지하며, Grinding으로 원하는 두께로 만듭니다. 그 후 CMP를 통해 Grinding 한 부분의 표면을 매끄럽게 만들어주고, Chip Dicing을 준비합니다.

CMP(Chemical Mechanical Polishing): 화학, 기계적으로 표면을 평평하게 만드는 공정으로 평탄화가 이뤄져야 포토공정에서 단차 문제가 해소됨, Stacking이 많을 수록 사용량이 증가합니다. 최근 TSV 공정 기술의 수요 증가로 사용량이 증가하고 있습니다.

- Dicing:

Wafer Sawing 단계이며, Chip을 하나하나 개별화하는 Singulation 공정

Grinding과 CMP 공정을 마친 Wafer를 Chip 단위로 자르는 공정이며, Laser나 톱을 이용해 절단합니다.

- 공정 종류: Blade, Laser, Plasma

위의 사진 처럼 순서대로 Dicing 방식이 발전해왔으며, 웨이퍼 두께가 얇아지면서 Plasma 방식으로 발전하고 있습니다.

Wafer Level Package에서는 DBG(Dicing Before Grinding)을 사용합니다.

- Die Attach 및 Bonding:

Wafer에서 잘라낸 Chip을 붙이는 공정, 또한 전기적 연결을 만들어주기 위해 Bonding을 진행

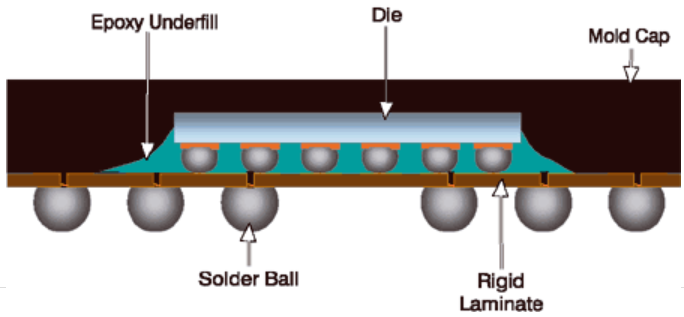

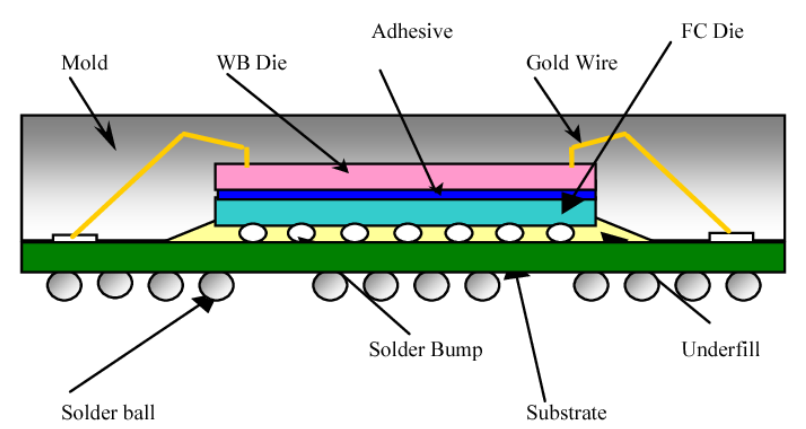

Bonding은 크게 2가지로, Wire Bonding과 Solder Bump로 나뉜다. 여기서의 차이로 Package의 종류를 나눌 수 있습니다.

Wire Bonding은 Stacking이 편하지만, 높은 인덕턴스를 가지기에 현재 해결해야할 과제입니다.

이에 반해, Filp Chip은 높은 I/O를 가지고, 신호의 길이가 짧아 임피던스가 좋습니다. 또한, 크기를 줄일 수 있고, 방열기능도 수월해 Wire Bonding에 비해 좋은 평가를 받고 있습니다. 하지만, Filp Chip 위에는 추가적으로 Stacking이 불가능합니다.

서로의 단점을 해결하기 위하여, Wire Bonding + Flip Chip을 Stacking 하는 패키지를 사용해 장점을 살리고 있습니다.

추가적으로,

Lead Frame 방식의 삽입실장형(DIP), 표면실장형(QFP)가 있지만, 기술 발전으로 현재는 많이 사용되지 않고 있습니다.

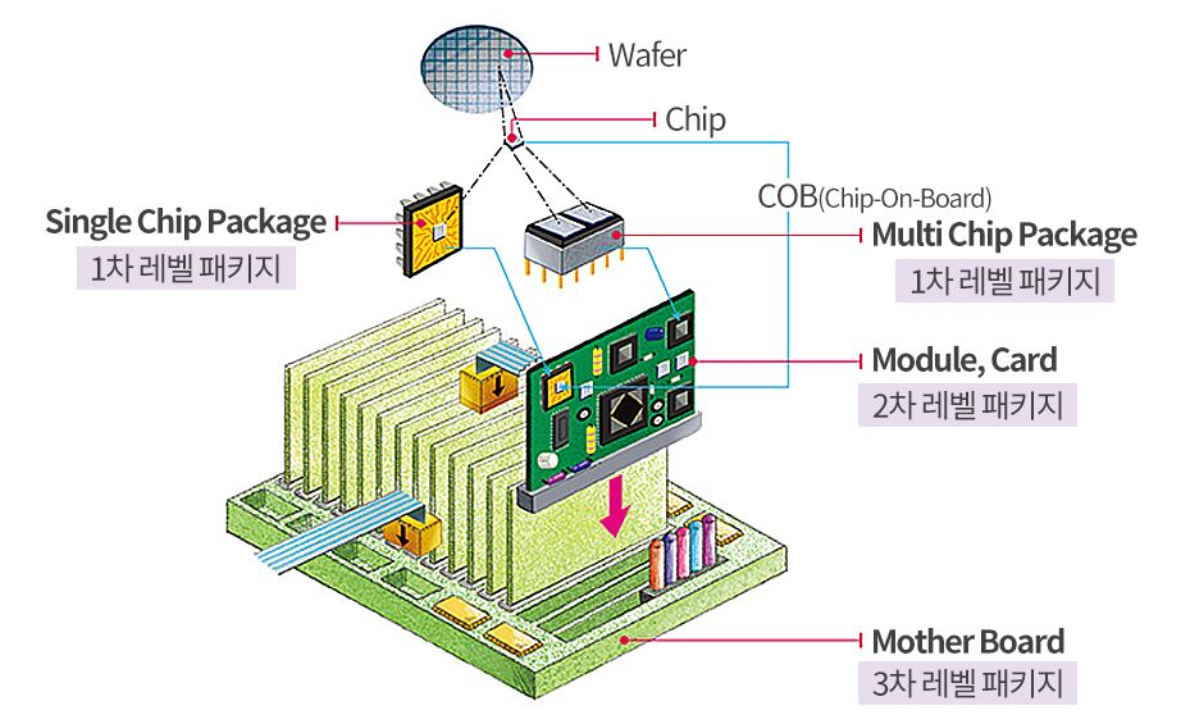

4. 패키지 레벨

반도체 패키지는 레벨에 따라 부르는 제품을 다르게 표현합니다.

Level 1: Integrated Circuit / IC 캐리어 역할

Level 2: Multi-Chip Module / IC Chip들을 조립할 수 있고, 구성 요소의 상호 연결이 가능, 하나의 시스템 형성

Level 3: PCB, Mother Board / Module들을 조립하여, 최종 제품을 구성할 수 있게 연결이 가능한 보드

Level 4: System / 최종 제품을 칭함

※이는 System-Level Integration의 방향으로 발전 방향을 보여주며, 2.5D/3D Package 방식으로 발전했습니다.

또한, 공정 순서로 Package를 구별합니다.

Chip-Level Package: Wafer를 Chip으로 먼저 자르고 Packaging을 진행하는 공정(Conventional)

-> Lead Frame, Substrate가 있습니다.

Wafer-Level Package: Packaging을 하고 Chip을 자르는 공정(Advanced)

-> RDL, FCBGA, TSV, Fan-out WLP가 있습니다.

다음 글에서는 표면실장 기술(Bonding 방법)에 대해서 구체적으로 정리하도록 하겠습니다!!

'반도체 패키지 > Advanced Package(AVP)' 카테고리의 다른 글

| HBM3E의 AP-FoM(TSMC) 기반 성능 평가 및 분석 (2) | 2024.06.16 |

|---|---|

| (삼성전자)HBM 16H Stacking을 위한 D2W HCB(하이브리드 본딩) (0) | 2024.06.13 |

| 표면실장 기술 - Soldering & 기타 Bonding (0) | 2024.01.19 |

| 표면실장 기술 - Bonding(Wire Bonding, Flip Chip Bonding) (0) | 2024.01.19 |

| Advanced Package(AVP) 기초 (0) | 2024.01.13 |